Lectures: WF 11:30 - 12:45, 217 College

Center

Course Description:

What goes on behind the scenes after you compile your

program? Students learn how a computer is put together,

and the relationship between the hardware and the instruction

sets. We study the MIPS machine language and the high

level organization of a fully pipelined modern RISC

machine: including: ALU design, CPU design, pipelining,

memory organization, cache and virtual memory, I/O, and methods

of measuring the effectiveness of these features.

Exams: There will be one midterm (25% -

100 points) and one final examination (35% - 140 points).

The final will be on Monday, May 6, 1:30 PM.

Assignments: Homework assignments and

programs are worth 40% (160 points) of your grade. You

should do these with a partner, and one grade will be given to

both people in each group.

Notes about software: All programs should be written using SPIM or MARS, both simulators for the MIPS architecture. You can download MARS or SPIM for whatever computer you own. PCSpim, an old version of SPIM for PCs, should already be loaded on the machines in the lab and it is what I use, but there is a new multi-platform version called QtSpim.

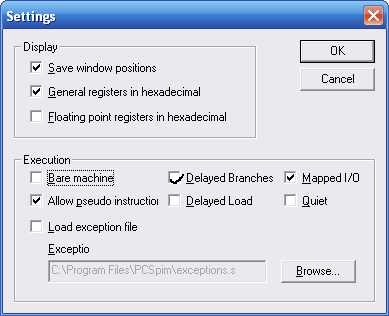

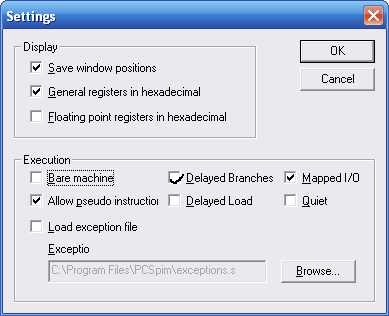

Technical details: If you download PCSpim, make sure that the settings are set as shown below so that the programs I run in class will all work. Delayed branches is kind of "half-checked". Theoretically, to get authentic assembly translation, it needs to be checked, but practically, to run a program it is easier to leave it unchecked, or else you will need blank "nop" instructions after every branch. Best to leave it unchecked if in doubt, or ask me. Delayed branches are a complicated idea that we cover late in the course, after you have been programming for weeks. In QtSpim, you need to uncheck MappedI/O. This makes sure you can see input typed in the console. MARS has a box to check in the settings that accomplishes the same thing and prints nice prompt messages for syscalls. If you get an error message in QtSpim saying that __start label is defined twice, try replacing __start: with main:

You should demo your programs for me personally. For written

problem sets, you should hand them into me personally (before midnight

of the day they are due). Late assignments will not be accepted or graded.

Finally, read our department's academic

integrity

guidelines before you submit any written work or

demonstrate any programs.

Grading: Your grade is 25% midterm, 40% homework, and 35% exam. The maximum points is 400. You can guarantee an A- or better with 90% (360), a B- or better with 80% (320) etc. I may curve these numbers in your favor, if I feel it is warranted.

Special Dates: Wed.

April 24 is Passover and I will not be in class. I

will remind you as we get close to the date.

MIPS Reference: Quick Reference MIPS Opcode LookUpCalculators: Decimal-Binary-Hex Converter IEEE754 Floating Point Calculator Desmos Graphing Calculator

"Cheat Sheet"MIPS Reference (Green Card from the text for use on exams)

Reading Assignments: These readings explain why programmers should know architecture. Read them the first week of class, and read them again after the tenth week. I mean that! You will learn a lot each time. If you get anything out of this class, it should be the notion that computer architecture is important for programmers!

Read Understanding Quakes' Fast Inverse Square Root. For you game players -- this short article explains how to use the IEEE 754 floating point format to extract an exponent to get a great first guess for an inverse square root, an operation crucial to graphics rendering in games. What used to require special processing and graphics cards became a one-line software hack! Here is video for those of you who prefer. And, this paper shows just how clever and complex is the choice of the "wtf" number 0x5f3759df. Read through this StackExchange forum on sorted arrays and branch prediction. Read this article on how Apple's new M1 chip architecture is leaving Intel/AMD chipsets in the dust, something you game players might care about. This article touches on almost every major concept we study in this course: pipelining, control, data path, cache design, RISC/CISC, etc.

Written Assignments and Programming: Assignment 1 Assignment 2 Assignment 3 Assignment 4 Assignment 5 Assignment 6 Assignment 7

Week |

Topics |

Reference

|

| 1 | CISC versus RISC. Measuring Performance. Why do Programmers Need to Know About Computer Architecture? |

Chapter 1, Hsieh, StackExchange, Apple's M1 chip, Quake Square Root |

2-4 |

Intro to SPIM Simulator Basics: Instructions, Data, and Directives. Basic MIPS Assembly Language: Arithmetic and Memory Operations, Control Structures: Ifs and Loops. Arrays. Strings IO Multiply Avg Traverse_array Address modes Branches Loops Palindrome Long_mult Sort |

Chapters 2 and 3, QtSpim/MIPS manual |

| 5 |

Data Representation - Two's

complement, Sign Magnitude, Floating Point, ASCII.

Bit-operations:

and, or, not. Shift and Rotate operations. IEEE

754 details. MIPS Floating Point and IEEE 754 |

Chapter 3 |

| 6-7 | More MIPS: Registers and Address Modes. Data Structures, 2D-arrays, Objects, Stacks, Procedures, Stack Frames, Run-time Stack, Parameter Passing. Methods in MIPS: Recursive Factorial and Stack Trace MIPS_Translation_Example |

Chapter 2, Appendix A: 5-11 |

| 8 |

Machine Language and MIPS Instruction Formats. Assemblers - One and Two Pass. |

Chapter 2, Appendix E.1-3, Appendix A:1-4 |

9 |

Midterm Examination. |

Friday, March TBA |

My Notes above and the embedded links below are very useful reading for the rest of the course. They will allow you to take notes much more easily. |

||

10 |

Data Path and Control Architecture - Single versus Multi-cycle. MultiCycleDataPath FiniteStateMachineMultiCycle SingleCycleDataPath Practice Adding Instructions to MultiCycle Implementation |

Chapter 4: 1-4, Appendix D: 1-5, |

| 11-12 | Pipelining - An Efficient CPU, Performance Measures, Structural Hazards, Data Hazards, Forwarding, Branch Hazards, Hazard Handling: Forwarding, Branch Predictions, Compiler Rewrites, Stalls and No-ops. PipeliningDataPath PipeliningHazards DataHazard-Forwarding |

Chapter 4: 5-8 |

| 13-15 | Memory Architecture - Hierarchical Structures: Cache and Virtual Memory. Cache Review Slides Practice with Cache and Virtual Memory |

Chapter 5: 1-8 |

(If time allows) Cloud Computing and Parallel Processing |

Chapter 6 |